集成电路CAD设计 芯片焊盘与版图布局的核心技术与服务全览

集成电路(IC)是现代电子设备的“大脑”,其设计过程高度复杂且精密。计算机辅助设计(CAD)技术在这一过程中扮演着至关重要的角色,它贯穿了从概念到物理实现的每一个环节。本文将聚焦于集成电路CAD设计中的两大关键部分——芯片焊盘设计与版图布局设计,并概述相关的设计服务生态。

一、 芯片焊盘设计:连接芯片与外部世界的桥梁

焊盘(Pad)是芯片上用于与外部封装引脚或直接与电路板进行电气连接和机械固定的金属区域。其设计质量直接影响到芯片的可靠性、信号完整性和可制造性。

- 功能与类型:焊盘不仅负责传输电源、地信号和各种输入/输出(I/O)信号,还包括用于芯片测试的专用焊盘。主要类型有电源/地焊盘、信号I/O焊盘、模拟焊盘(对噪声更敏感)以及用于晶圆级测试的探针焊盘。

- 设计考量要素:

- 电气特性:需考虑电流承载能力、电感、电容和电阻(ESD保护)等,确保信号质量并防止静电损伤。

- 几何尺寸与间距:必须严格遵守设计规则(DRC),满足光刻和封装工艺的极限要求,防止短路或断路。

- 布局规划:焊盘通常沿芯片周边(外围布局)或分布在整个芯片表面(阵列布局)排列。布局需优化信号路径,减少串扰,并考虑封装引线键合或倒装芯片凸点(Flip-Chip Bump)的可行性。

- 可靠性:涉及金属电迁移、热机械应力分析等,确保在长期使用和温度变化下的稳定性。

二、 版图布局设计:将电路图转化为物理蓝图

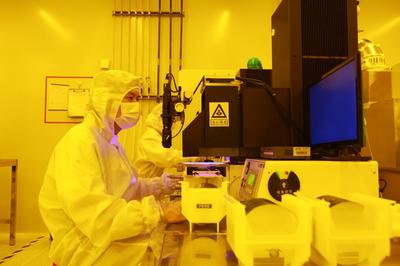

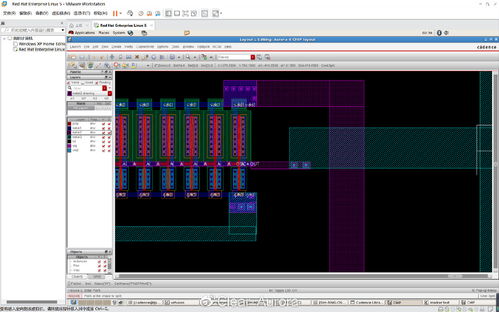

版图布局(Layout)是将逻辑电路图(原理图)转换为一系列几何图形(多晶硅、金属连线、接触孔等)的过程,这些图形定义了制造芯片时各层掩模的图案。这是CAD设计的核心环节。

- 设计流程:通常从模块布局开始,进行单元(标准单元或模拟单元)的放置,然后进行详细的布线连接,最后进行严格的物理验证。

- 核心目标与挑战:

- 性能优化:通过精心布局布线,最小化关键路径的延迟,降低寄生电容和电阻,提升芯片速度。

- 面积优化:在满足性能的前提下,尽可能缩小芯片面积以降低制造成本。

- 功耗管理:合理的电源网络设计和时钟树综合对控制动态与静态功耗至关重要。

- 可制造性设计(DFM):在版图中引入工艺考量,如添加冗余接触孔、考虑化学机械抛光(CMP)效应等,以提高实际晶圆生产的良率。

- 验证:必须通过设计规则检查(DRC)、版图与电路图一致性检查(LVS)以及电气规则检查(ERC)等,确保设计的正确性与可靠性。

三、 集成电路芯片设计及服务生态系统

随着工艺节点不断演进(如进入纳米级、FinFET时代),设计复杂度呈指数级增长,催生了一个庞大的专业设计服务产业。

- 设计服务范畴:

- 全流程设计服务:提供从规格定义、架构设计、RTL编码、逻辑综合、物理实现到最终签核的完整服务。

- 特定环节服务:专注于物理实现(即版图设计与验证)、模拟/混合信号设计、IP集成、可测性设计(DFT)或信号/电源完整性分析等。

- 先进封装协同设计:随着2.5D/3D IC和异构集成兴起,服务范围扩展到芯片-封装-电路板的协同设计与分析。

- 服务价值:

- 降低门槛与风险:帮助无晶圆厂(Fabless)公司或初创企业克服先进工艺的设计挑战,节省昂贵的工具投资和人才培养成本。

- 加速上市时间(Time-to-Market):凭借丰富的经验库和经过验证的设计流程,大幅缩短产品开发周期。

- 提升质量与良率:专业的DFM和验证实践能显著提升芯片的一次成功率(First Silicon Success)和生产良率。

结论

芯片焊盘与版图布局设计是集成电路CAD领域的技术基石,它们将抽象的电路思想转化为可制造的物理实体。在摩尔定律持续推进和系统复杂度激增的背景下,这两项工作的挑战日益严峻。与此专业、高效的集成电路设计服务已成为产业不可或缺的支撑力量,它赋能创新者,推动着从消费电子到人工智能、汽车电子等前沿领域的芯片创新与落地。掌握这些核心技术与善用专业服务,是企业在激烈竞争中制胜的关键。