一口气带你搞懂芯片设计制造全流程 从创意到晶体管的奇妙之旅

你是否曾好奇,智能手机、电脑乃至汽车里的“大脑”——芯片,究竟是如何从工程师的创意变成手中那枚精密的硅片?这个过程复杂而精密,融合了人类智慧的巅峰与工业制造的极限。让我们一起,一口气理清芯片设计与制造的核心流程,揭开集成电路的神秘面纱。

第一阶段:芯片设计——在虚拟世界构建“城市蓝图”

芯片设计是整个流程的起点,如同为一座超级复杂的微型城市绘制蓝图。这个过程通常由集成电路设计服务公司或无晶圆厂(Fabless)半导体公司完成。

- 系统架构与规格定义:根据芯片的最终用途(如手机处理器、AI加速器),确定其性能、功耗、成本等关键指标。这好比确定城市是金融中心还是工业基地。

- 前端设计(逻辑设计):

- RTL编码:设计师使用硬件描述语言(如Verilog或VHDL),将芯片功能转化为代码,描述其寄存器传输级逻辑。这相当于编写城市的交通规则与建筑功能。

- 逻辑综合:通过EDA(电子设计自动化)工具,将RTL代码转换为由标准逻辑单元(如与门、或门)组成的门级网表。这是将抽象规则转化为具体的建筑模块清单。

- 功能验证:通过仿真和形式验证等方法,确保设计在逻辑上完全正确,功能符合预期。相当于对蓝图进行无数次模拟推演,确保城市运转无误。

- 后端设计(物理设计):

- 布图规划:在芯片的硅片“画布”上,规划各个功能模块(如CPU核心、内存控制器)的摆放位置,决定芯片的初步轮廓。

- 布局与布线:将数百万乃至数十亿个晶体管单元精确放置,并用极其细微的“导线”(金属互连层)将它们按照网表连接起来。这是最精密的“城市规划”与“道路施工”,需要平衡性能、面积和功耗。

- 物理验证与时序签核:检查设计是否满足制造工艺的物理规则(如线宽、间距),并确保信号在芯片内传输的延迟满足要求。这是蓝图交付制造前的最终质检。

- 最终输出的是 GDSII 文件,这是一套记录了每一层掩膜版几何图形的数据库,是交付给芯片制造厂的“最终施工图纸”。

第二阶段:芯片制造(流片)——在真实世界“雕刻”硅晶

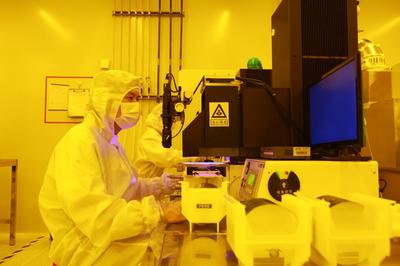

制造环节由晶圆代工厂(Foundry,如台积电、三星)完成,是将GDSII图纸实体化的魔法过程,在极度洁净的晶圆厂内进行。

- 掩膜版制作:根据GDSII文件,为每一层电路图形制作一套昂贵的母版——掩膜版,如同制作用于批量印刷的胶片。

- 晶圆制造:以高纯度硅圆柱切割出的薄圆片(晶圆)为基础,通过数百道精密工序逐层构建电路。

- 核心工艺:主要包括 光刻(通过掩膜版将图形“曝光”到涂有光刻胶的晶圆上)、刻蚀(将图形刻入硅片或薄膜)、离子注入(掺杂改变半导体特性)、薄膜沉积(生长或铺设各种材料层)这四大类操作的循环往复。

- 这个过程是在纳米尺度上(如今已进入3纳米、2纳米时代)的立体雕刻,最终在晶圆上形成数十亿个晶体管和复杂的互连网络。

- 晶圆测试:制造完成的晶圆会进行电性测试,用探针卡触碰芯片的焊盘,标记出功能正常的芯片(裸片)。不合格的裸片会被记录,后续舍弃。

第三阶段:封装与测试——赋予芯片“身体”与“体检”

- 封装:将测试合格的裸片从晶圆上切割下来,安装到封装基板上,用细金属线或凸块将其电路连接到外部引脚,然后用保护性外壳(通常是塑料或陶瓷)密封起来。封装保护了脆弱的硅片,并提供了与电路板连接的物理接口。

- 最终测试:对封装好的芯片进行全面的功能和性能测试,确保其在各种速度和温度条件下都能稳定工作。只有通过所有测试的芯片,才会被分级并打上标识,最终出货给电子设备制造商。

贯穿全程的“灵魂”:EDA工具与IP核

EDA工具:芯片设计极度依赖EDA软件(来自新思科技、楷登电子等公司),它们提供了从设计、验证到仿真的全套工具链,是设计师的“神笔”。

IP核:为了提升设计效率,设计中会大量使用预先设计好、经过验证的功能模块(如ARM的CPU核心、各种接口协议IP),如同建筑中的预制件,可以直接“集成”到芯片蓝图中。

**

芯片的诞生,是一场跨越虚拟与物理世界的漫长接力:设计公司 负责构思与绘制蓝图(设计),晶圆厂 负责在硅片上微观雕刻(制造),封装测试厂 负责为其穿上铠甲并体检(封测)。而 EDA工具 与 IP核** 则是加速这一过程的催化剂。整个过程通常需要数百人历时1-3年,耗资数亿甚至数十亿美元。正是这环环相扣、精益求精的流程,才将沙粒(硅来源于石英砂)变成了驱动数字时代的智慧结晶。下次当你拿起手机,或许会对其中蕴含的这项人类工程学奇迹,多一份惊叹与理解。